DIGITIMES Research:封裝密度要求持續提高 晶片互連朝混合鍵合技術發展

DIGITIMES Research:封裝密度要求持續提高 晶片互連朝混合鍵合技術發展。(資料照)

DIGITIMES Research:封裝密度要求持續提高 晶片互連朝混合鍵合技術發展。(資料照)

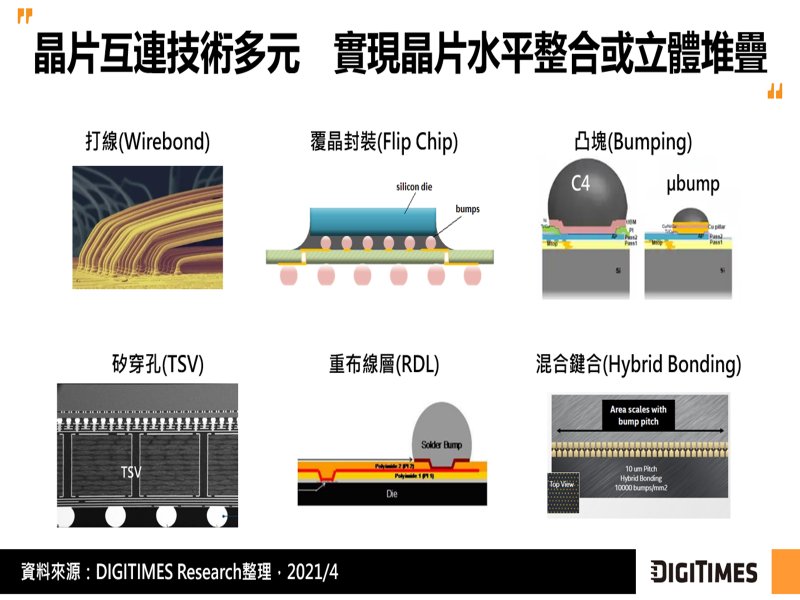

互連(interconnect)技術是晶片間的溝通橋梁,從傳統的打線(wire bond)、覆晶封裝(Flip Chip;FC)、微凸塊(µbump)到矽穿孔(Through Silicon Via;TSV)、重布線層(Redistribution Layer;RDL)、矽橋晶片(silicon bridge chip)等,滿足晶片效能持續提升需求;因應晶片朝更高密度整合趨勢,混合鍵合(hybrid bonding)將成新方案。

打線封裝、覆晶封裝雖是目前市場上IC主流互連技術,但在電子裝置體積與功能要求及晶片朝更高效能發展下,2.5D封裝所需的互連技術轉向以TSV、RDL為主,而矽橋晶片則是相對新興的互連解決方案。多數IDM、晶圓代工與委外半導體封測(OSAT)業者均已布局TSV、RDL技術,而英特爾(Intel)、台積電、矽品則另有矽橋晶片解決方案。

DIGITIMES Research分析師陳澤嘉表示,由於高效能運算(HPC)晶片對效能、封裝密度要求持續提升,微凸塊技術雖可實現HPC晶片3D封裝需求,但面對更高I/O數、更低功耗的發展趨勢下,混合鍵合技術因可進一步縮小鍵合間距(bond pitch),提高I/O密度、頻寬密度(bandwidth density)、降低功耗等優點,可望成為未來HPC晶片互連的新方案,吸引包含英特爾、台積電與格芯(GlobalFoundries)等業者投入混合鍵合技術開發。

打線封裝、覆晶封裝雖是目前市場上IC主流互連技術,但在電子裝置體積與功能要求及晶片朝更高效能發展下,2.5D封裝所需的互連技術轉向以TSV、RDL為主,而矽橋晶片則是相對新興的互連解決方案。多數IDM、晶圓代工與委外半導體封測(OSAT)業者均已布局TSV、RDL技術,而英特爾(Intel)、台積電、矽品則另有矽橋晶片解決方案。

DIGITIMES Research分析師陳澤嘉表示,由於高效能運算(HPC)晶片對效能、封裝密度要求持續提升,微凸塊技術雖可實現HPC晶片3D封裝需求,但面對更高I/O數、更低功耗的發展趨勢下,混合鍵合技術因可進一步縮小鍵合間距(bond pitch),提高I/O密度、頻寬密度(bandwidth density)、降低功耗等優點,可望成為未來HPC晶片互連的新方案,吸引包含英特爾、台積電與格芯(GlobalFoundries)等業者投入混合鍵合技術開發。